| MATLAB HDL Coder从入门到翻车(一) | 您所在的位置:网站首页 › hdl parameter › MATLAB HDL Coder从入门到翻车(一) |

MATLAB HDL Coder从入门到翻车(一)

|

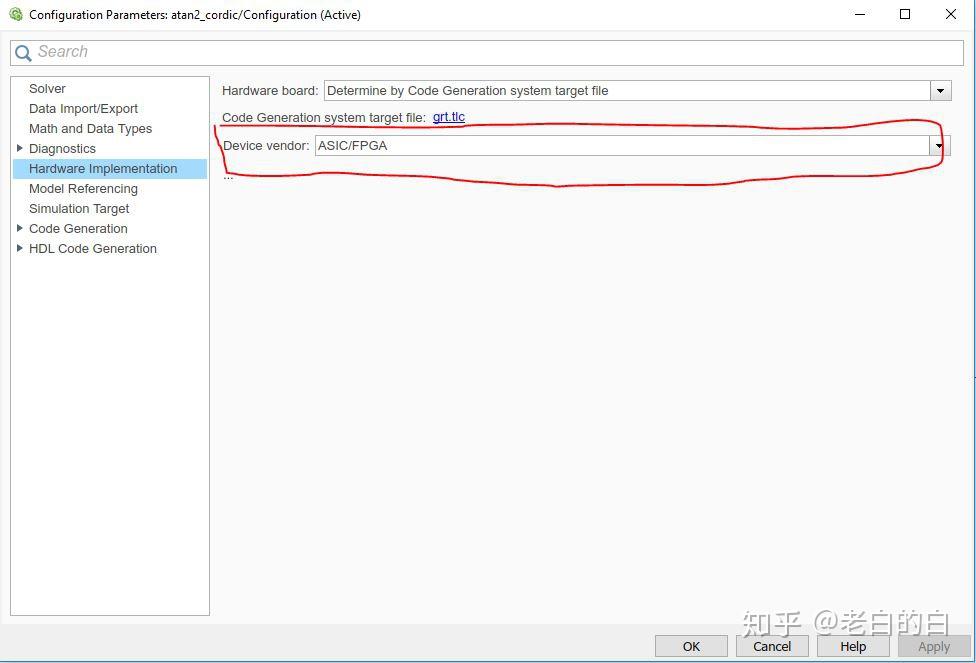

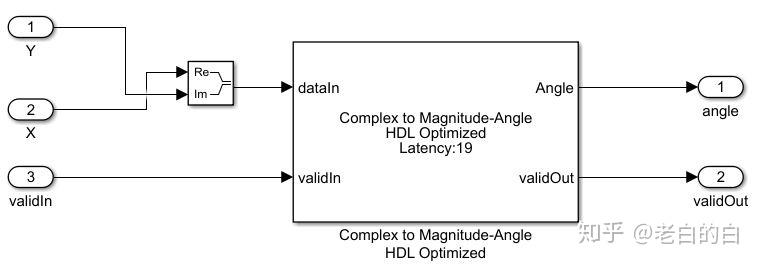

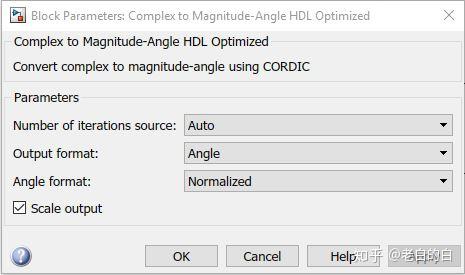

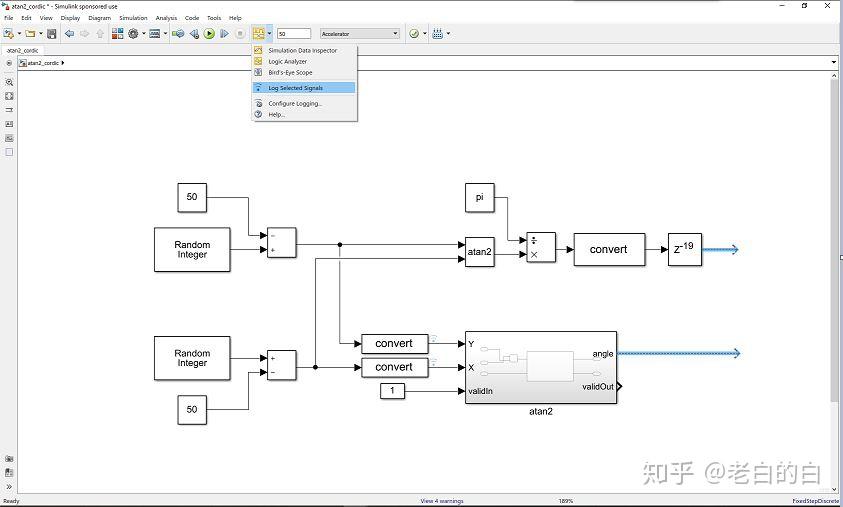

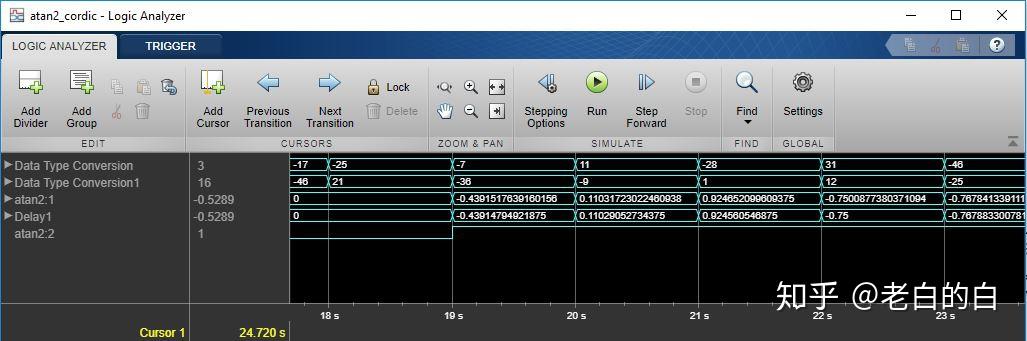

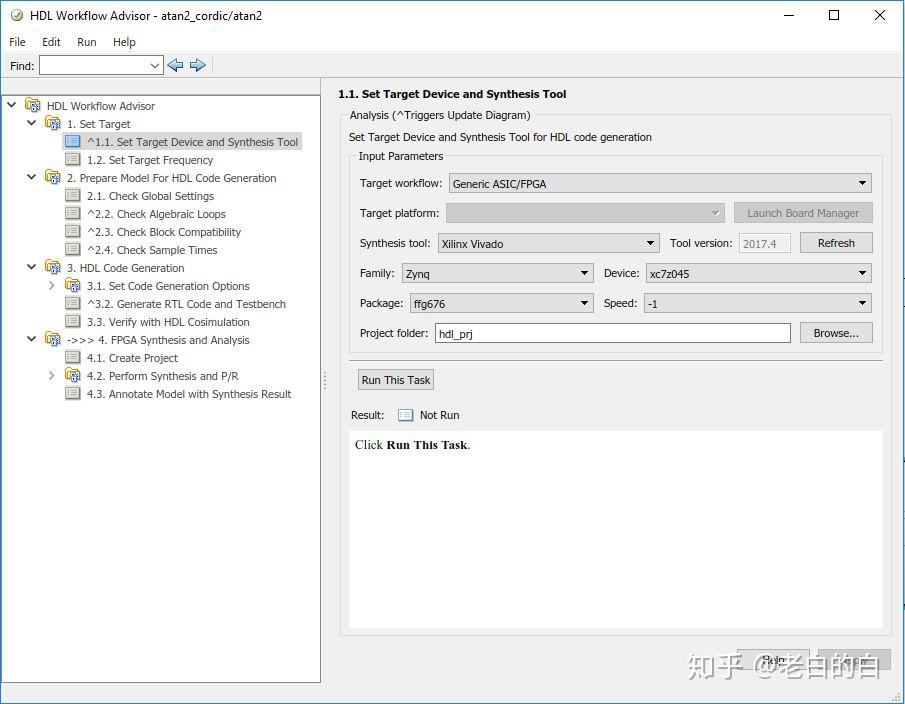

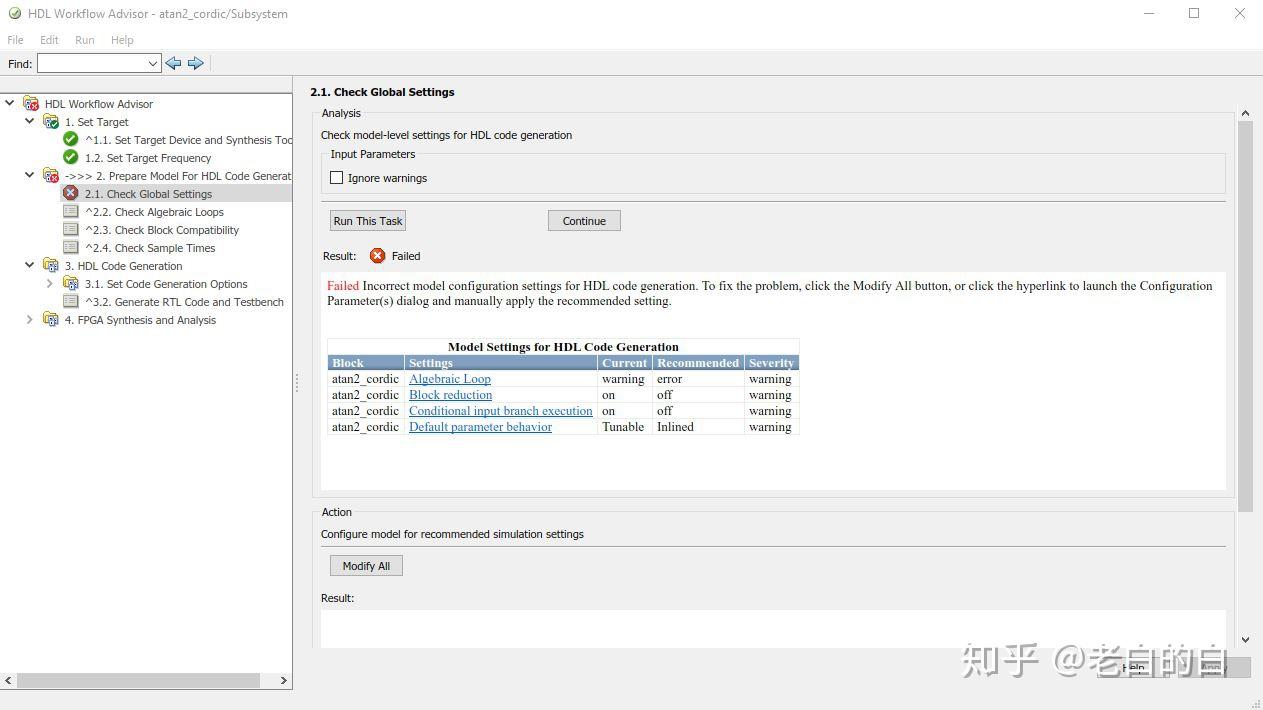

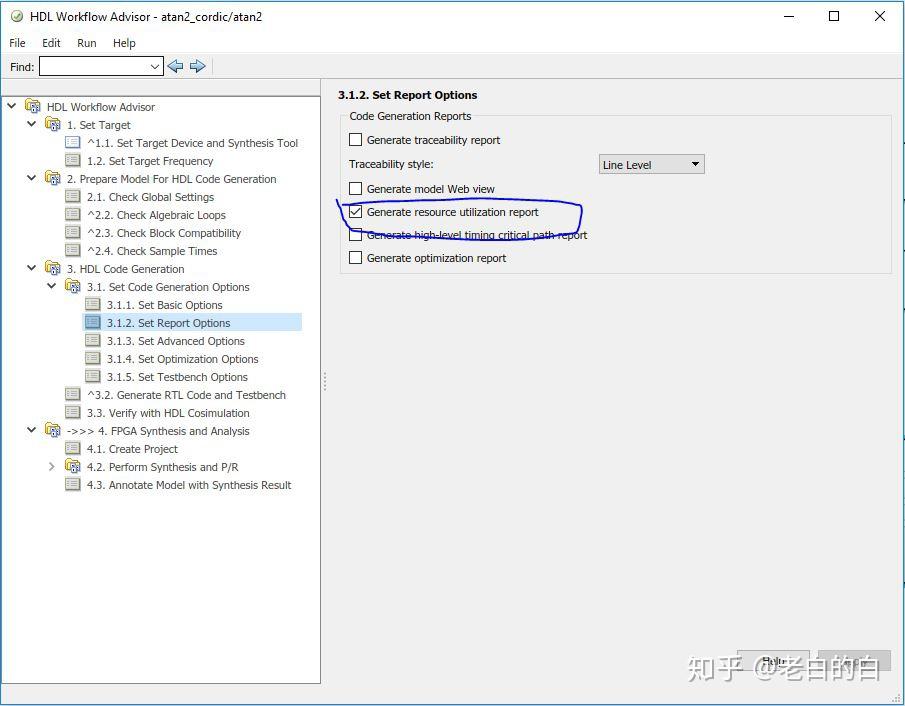

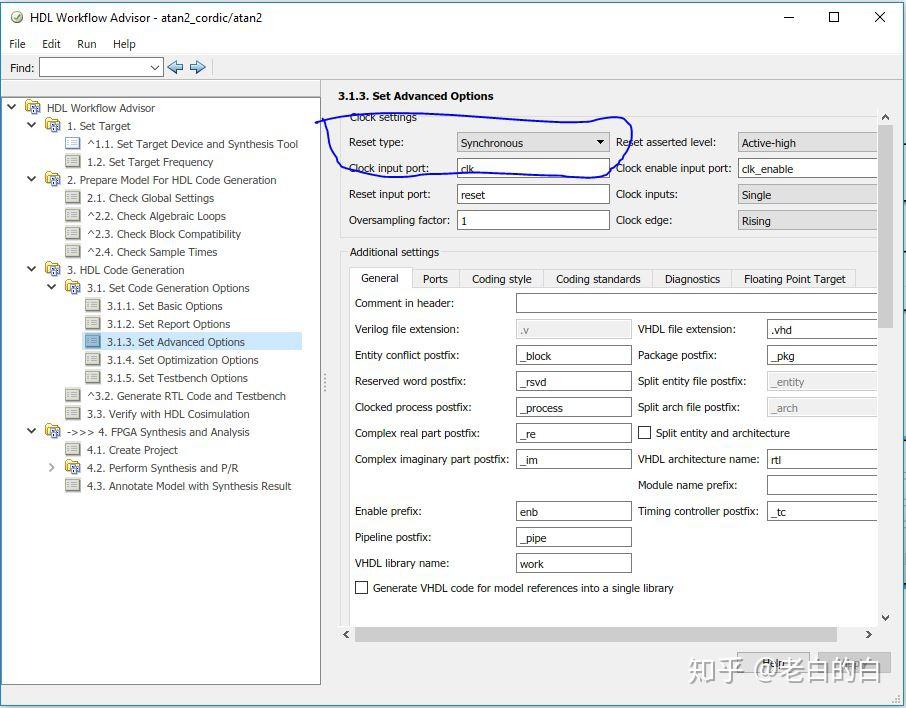

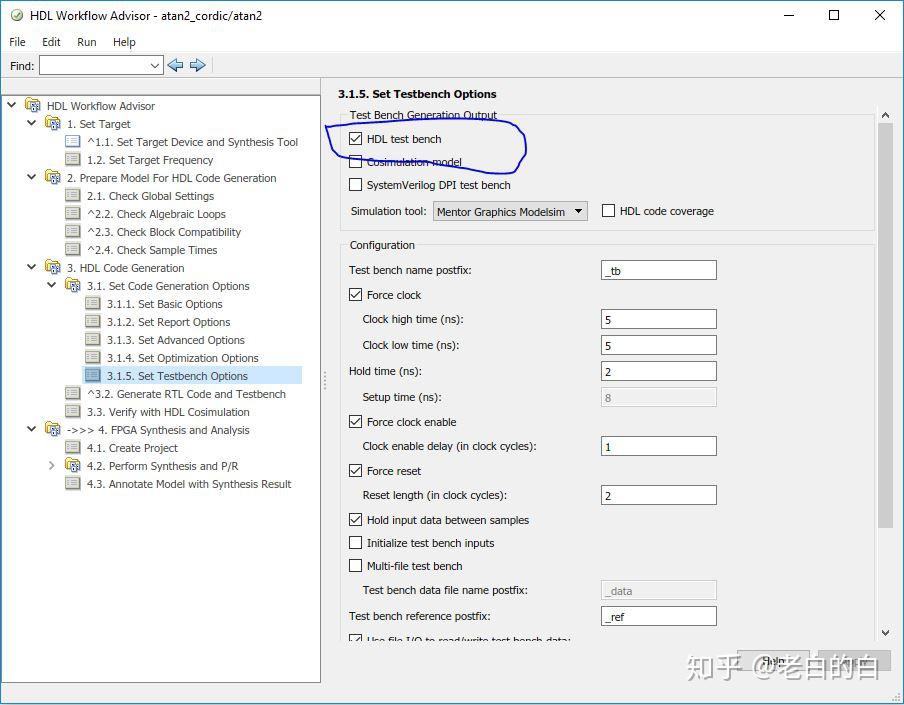

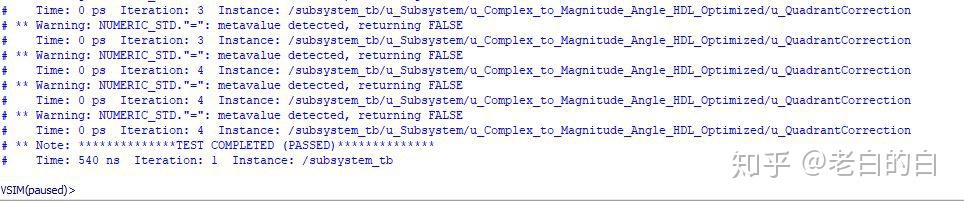

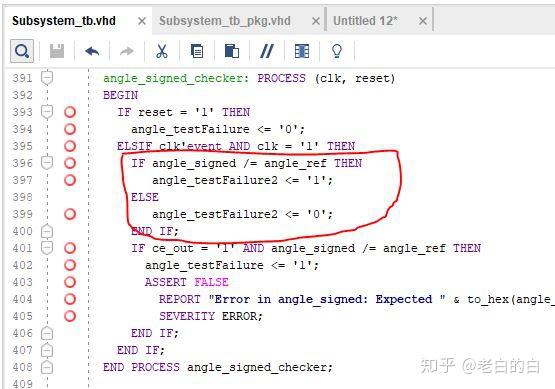

更新:本文所用的Simulink Model请移步我的Github下载。 最近一直在给大家洗脑,MATALB HDL Coder+Simulink对于视觉开发人员来说比Vivado HLS更加友好。但是Mathworks的example一如既往的对新手不友好,所以从现在开始我不定期的更新入门教程,希望能帮助到感兴趣的人群。 第0章:环境搭建 所需软件版本:MATLAB 2018b,+ HDL Coder Toolbox。文本假定读者有基本的独立运行Vivado工程进行仿真,综合的能力。 我们先创建一个新的Simulink model,由于这次的实例是基于CORDIC的atan2函数实现,所以我们将这个新model文件命名为“atan2_cordic.slx“。 首先,点击右下角VariableStepAuto(下图),再点击齿轮按钮打开Configuration Parameters菜单。  1)按照下图中圈1和圈2将Simulink环境配置成为定点离散环境,圈3一般不用改成1,但如果你遇到错误提示你的solver不是1的时候,把这个auto改成1可能会拯救你的模型。  2)缺省的Hardware Implementation选项是面向x86-64系统的,我们需要将它改成ASIC/FPGA。  至此,我们的Simulink环境配置就做完了。可以开始搭建我们的模型了。 第1章:第一个HDL Coder模型 - 基于流水线CORDIC的atan2函数实现 1.1 模型搭建 我们的设计分成三个部分:a)仿真数据生成,b)浮点验证部分,c)HDL Coder atan2模型 所以目标模型长这个样子,蓝色部分代表a)部分,红色代表b),绿色代表c)。  Q:如何添加模块?A:在空白处双击鼠标左键进行搜索 HDL Coder atan2模型如下图所示  下面详细介绍各部分: 双击空白处并键入Complex to Magnitude-Angle HDL Optimized,以及Real-Imag to Complex完成上图的模型搭建。双击CORDIC模型,来配置参数如下:  我们只要求角度,所以Output format选择Angle,Angle format随便选,此处我们选Normalized,意思是 [\pi,-\pi] 会被归一化至 [-1,1] 。Number of iterations source选择Auto,所需iteration和输入数据精度有关,暂时放在这里,之后会说。 这样,HDL coder模型就建好了。下面开始浮点验证部分。 依照上述方法搭建模块,由于atan2函数输出的是弧度值,所以我们需要除以 \pi ,将其归一化,并将其从double类型转换成(1,16,14)定点格式,以便在Logic Analyzer中显示。此处(1,16,14)表示1位的符号位,16位的总长度,小数位有14位。延迟19个时钟周期是为了使验证模型和HDL Coder模型同一时间输出数值。 仿真数据生成模块中,Random Integer随机输出 [0,99] 中的数,减去50,最终的输入数值区间为[-50,49] 。此模块中有两个convert模块,目的是为了将double 类型转换成定点数(1,16,8),符合HDL Coder模型对于输入的要求。 至此,模型搭建全部完成,下一步-仿真。 1.2 Simulink仿真 选中我们需要采集的信号并且如下图所示注册到Logic Analyzer中。  将所有我们需要注册的信号选中,开始仿真,点击仿真按钮,再点击Logic Analyzer按钮,就会弹出逻辑分析仪的窗口,如下:  可以看出,浮点的结果和我们HDL Coder模型的结果误差在一个很小的范围内。 下面开始重头戏。 1.3 生成HDL代码并仿真 首先设置Vivado路径,在MATLAB的Command Window中输入以下命令(路径设置为你电脑中Vivado的安装路径)  鼠标右键点击需要转换成HDL的模块,HDL Coder->HDL Workfow Advisor。  设置你的目标器件等,这里器件是什么并不重要,以后可以在Vivado里改。完成后点击Run This Task。在1.2中设置Target Frequency为50MHz。同1.1点击Run This Task。 步骤2的话,可以直接点击Run All。通常会出现如下Error,只是一些系统设置的要求,按照条目一条一条改过来即可。  HDL Coder Generation选项,3.1.2我们选择Generate resource utilization report。由于针对Xilinx器件,我们在3.1.3中将Reset Type设置为Sync类型。3.1.5选择生成HDL test bench。    3.2选中Generate test bench;3.3 选择Skip this task来略过Cosimulation,由于额外需要HDL Verifier toolbox,故不在此处讲解。 当跑完HDL Coder Generation部分之后,我们的代码就生成并且在MATLAB中仿真验证成功了。下面我们使用ModelSim来做功能仿真。代码存放在.\hdl_prj\hdlsrc\atan2_cordic中。将ModelSim的当前路径改变至代码存放文件夹,如 cd .\hdl_prj\hdlsrc\atan2_cordic 在运行如下命令   当ModelSim显示TEST COMPLETED (PASSED),则表明我们的功能仿真通过了  下面我们运行HDL Workflow Advisor的第4步,FPGA Synthesis and Analysis。一般我们只需要运行第一步生成Vivado工程,剩下的可以在Vivado内运行。 由于懒,我们不会把工程下载到板子上验证。所以只进行综合后时序仿真,如果通过我们就认为代码没有问题 当4.1完成后,打开Vivado工程并Run Synthesis。完成后,导入仿真代码(Subsystem_tb.vhd,Subsystem_tb_pkg.vhd)和数据文件(X.dat,Y.dat,angle_expected.dat,validOut_expected.dat)。 运行综合后时序仿真,下面就是见证翻车的时刻!!! 错误1:找不到work库,因为Vivado默认库被命名为xil_defaultlib。所以我们将仿真文件中所有的work改成xil_defaultlib。 错误2:意外发现时钟周期被改成10ns,所以我们将其改成20ns以对应50MHz的时钟。 再跑,就没问题了,但是!But!Aber! 惊奇的发现仿真正确的flag信号居然跳到了‘1‘!说明时序仿真错误!  经研究发现,这是因为angle和validOut信号被无故延后了3个时钟周期。但貌似后面的数值没有问题,所以我们添加了如下信号,来检测每一个计算出来的angle和angle_expected是否对应,相同则为0,不同则为1。再次仿真得到下图  所以我们判断,此处只是被加入了3个寄存器,atan2功能本身并没有问题。至于为什么加了三个节拍,我需要去问一下Mathworks工程师。 如果有好心人愿意帮我用ModelSim跑一下时序后仿,将感激不尽。毕竟我没有license。 以上就是今天的翻车记录。 |

【本文地址】